# The Impact of Memory Subsystem Resource Sharing on Datacenter Applications

Lingjia Tang, Jason Mars

Neil Vachharajani, Robert Hundt, Mary Lou Soffa

Friday, June 10, 2011

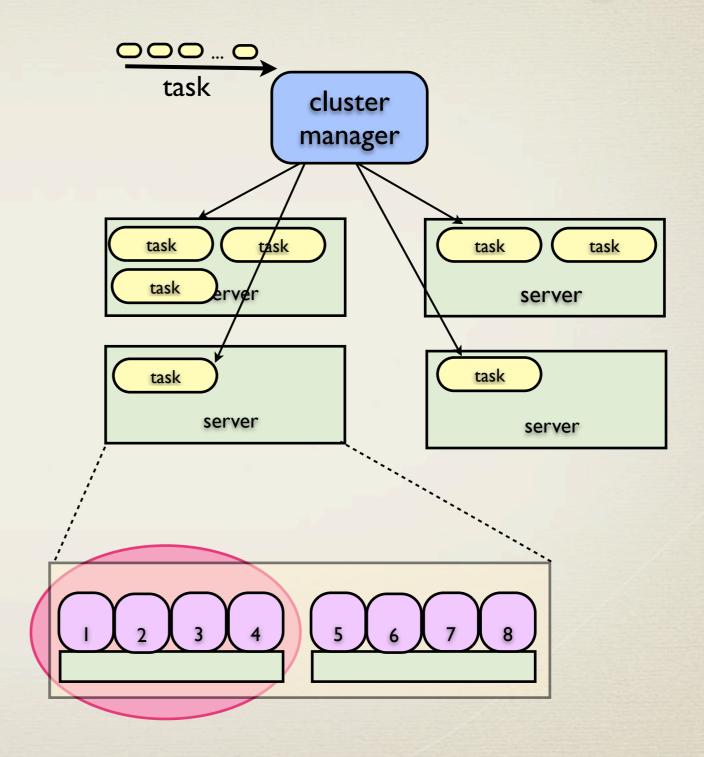

## Modern Datacenter

\* Datacenters: important computing domain

- \* Host large-scale internet service

- \* Expensive

#### Problem

- \* Lack of understanding of the datacenter workloads

- \* Emerging workloads (different than standard benchmarks SPEC, PARSEC, etc)

- \* How workloads interact with commodity multicore hardware (shared memory resources)

- \* How workloads interact with each other on multicores

- \* Lack of understanding leads to inefficient systems

- \* 1 % performance improvement is huge at Google's scale

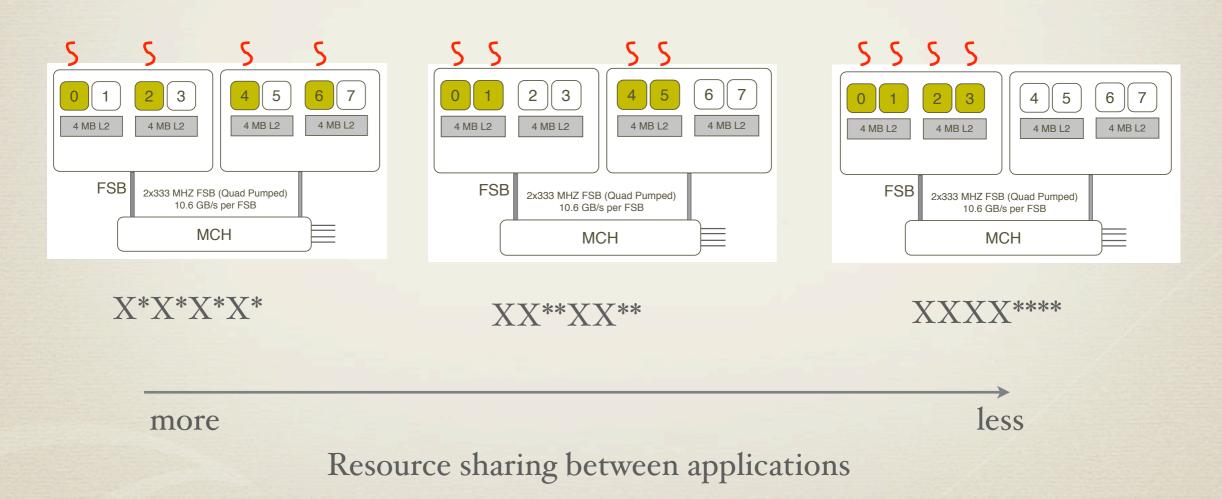

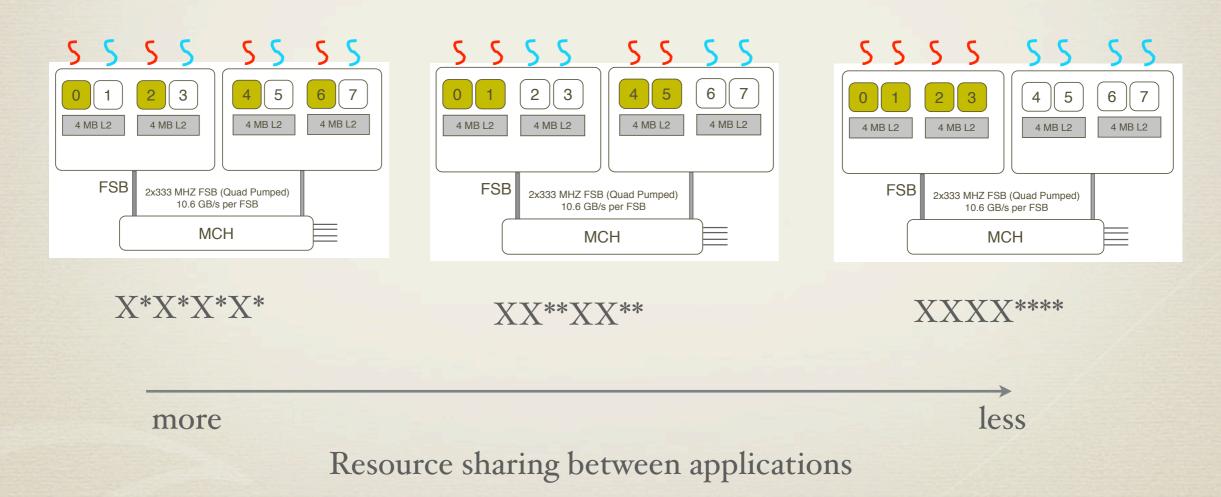

\* Sharing: constructive and destructive

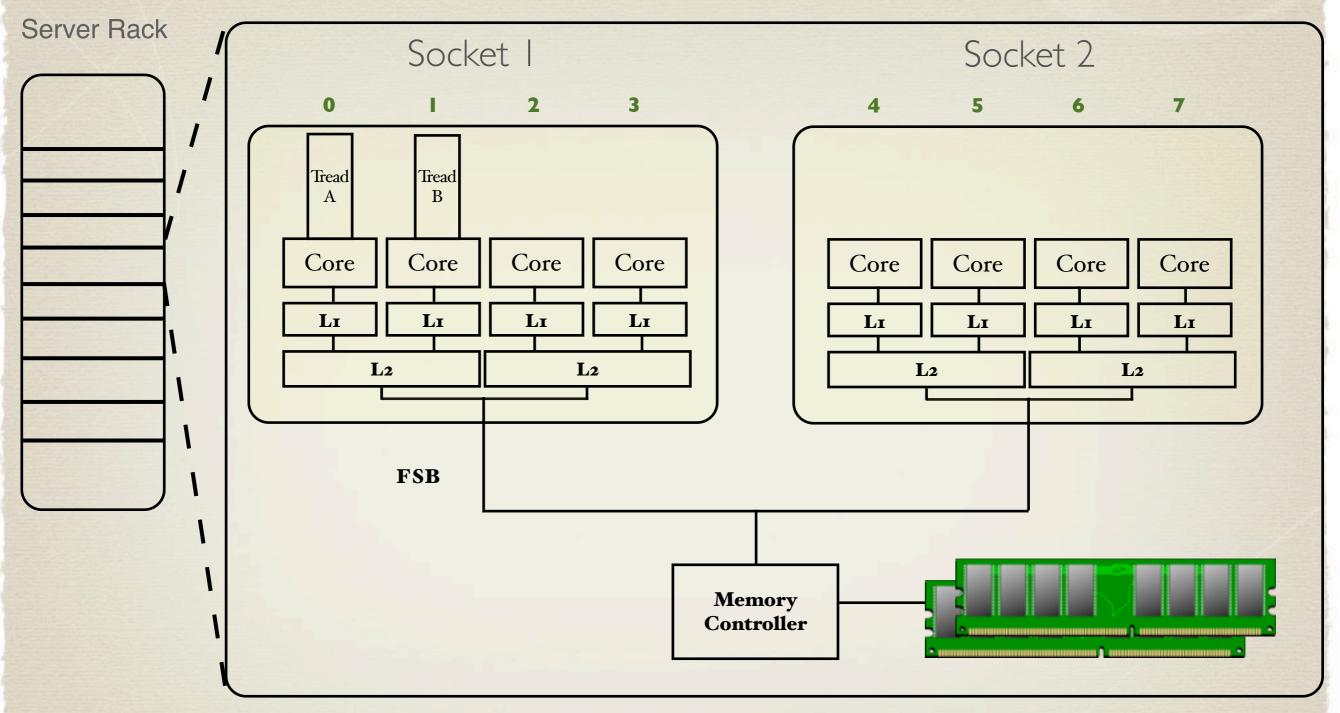

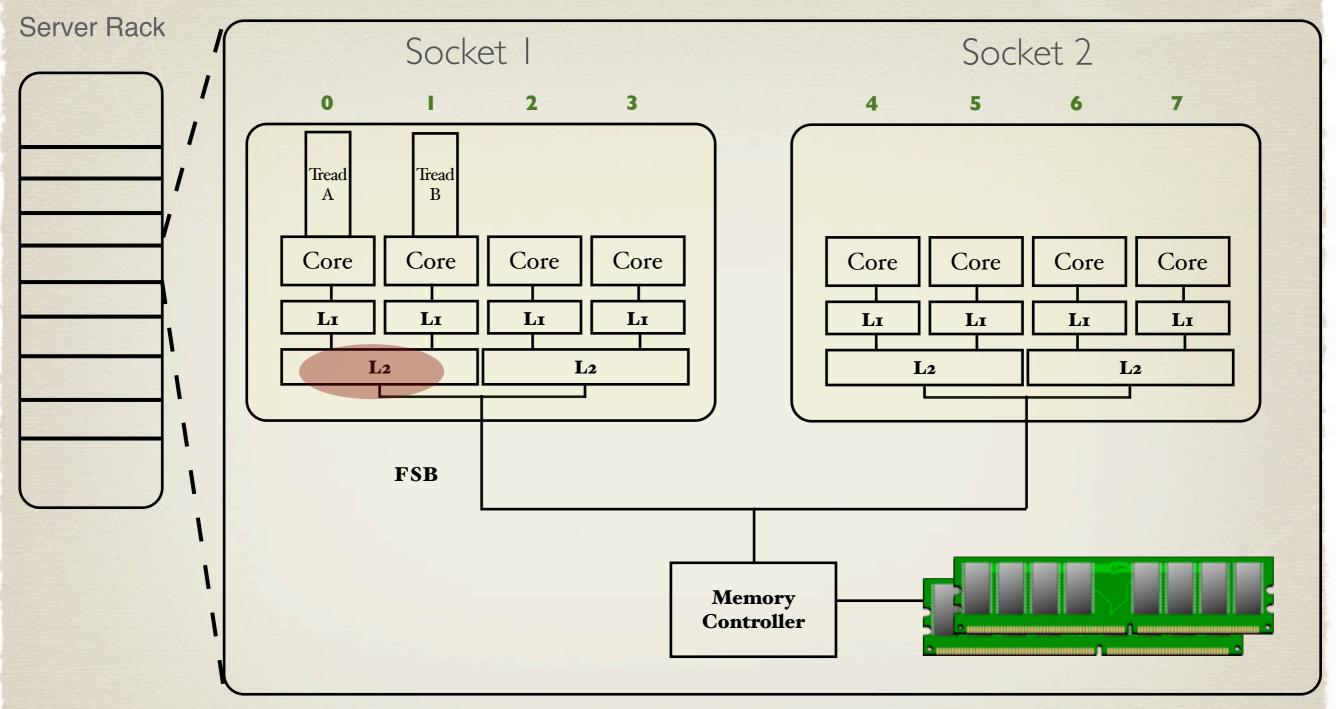

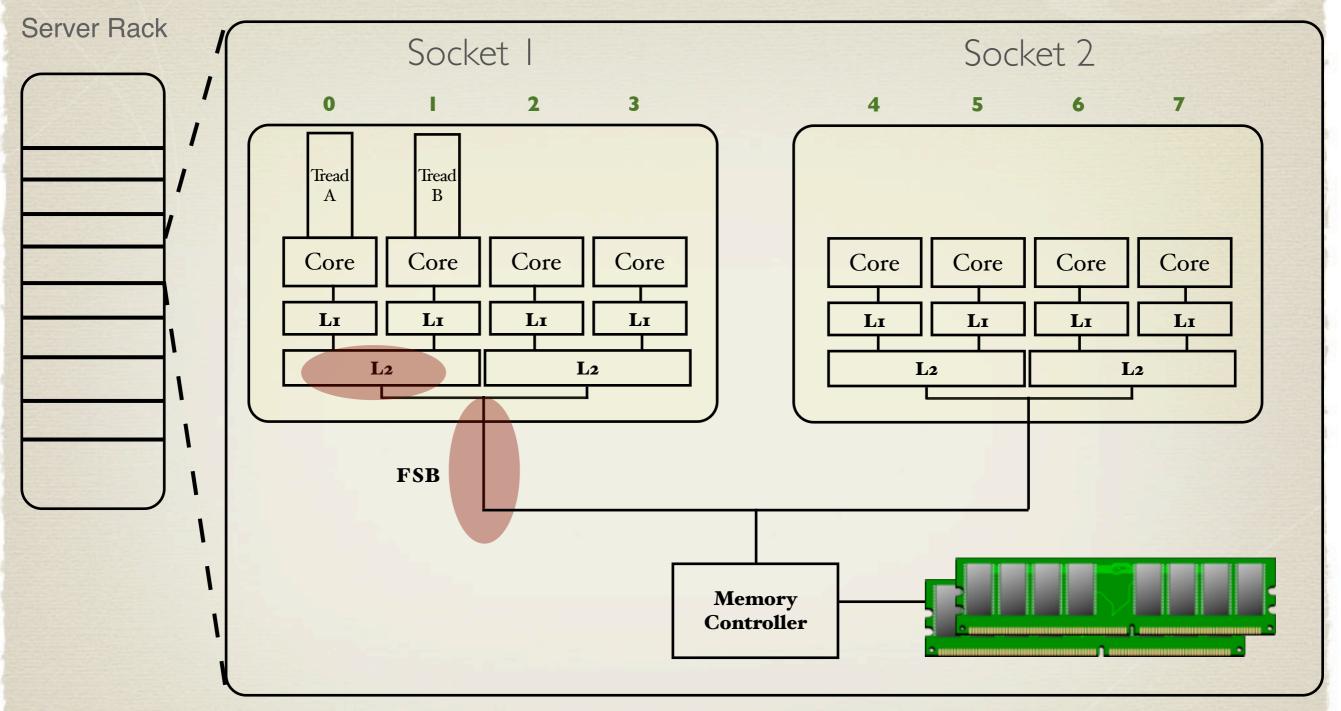

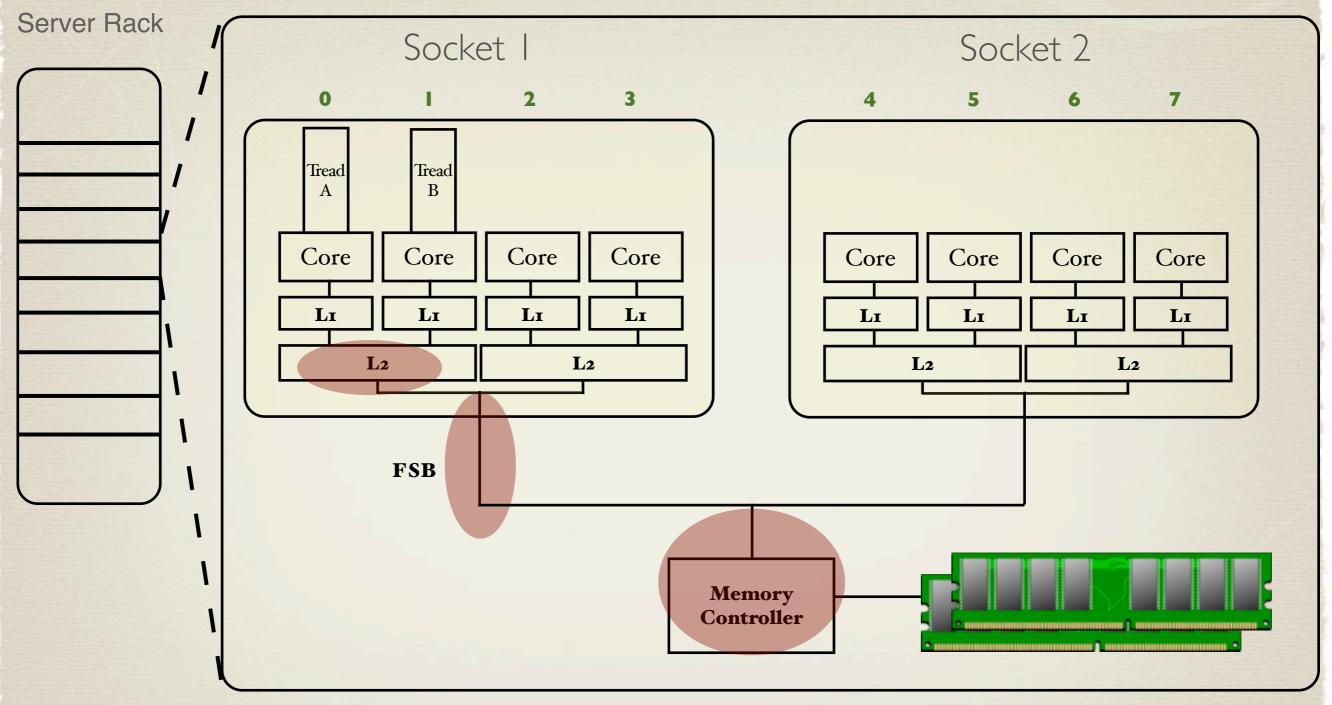

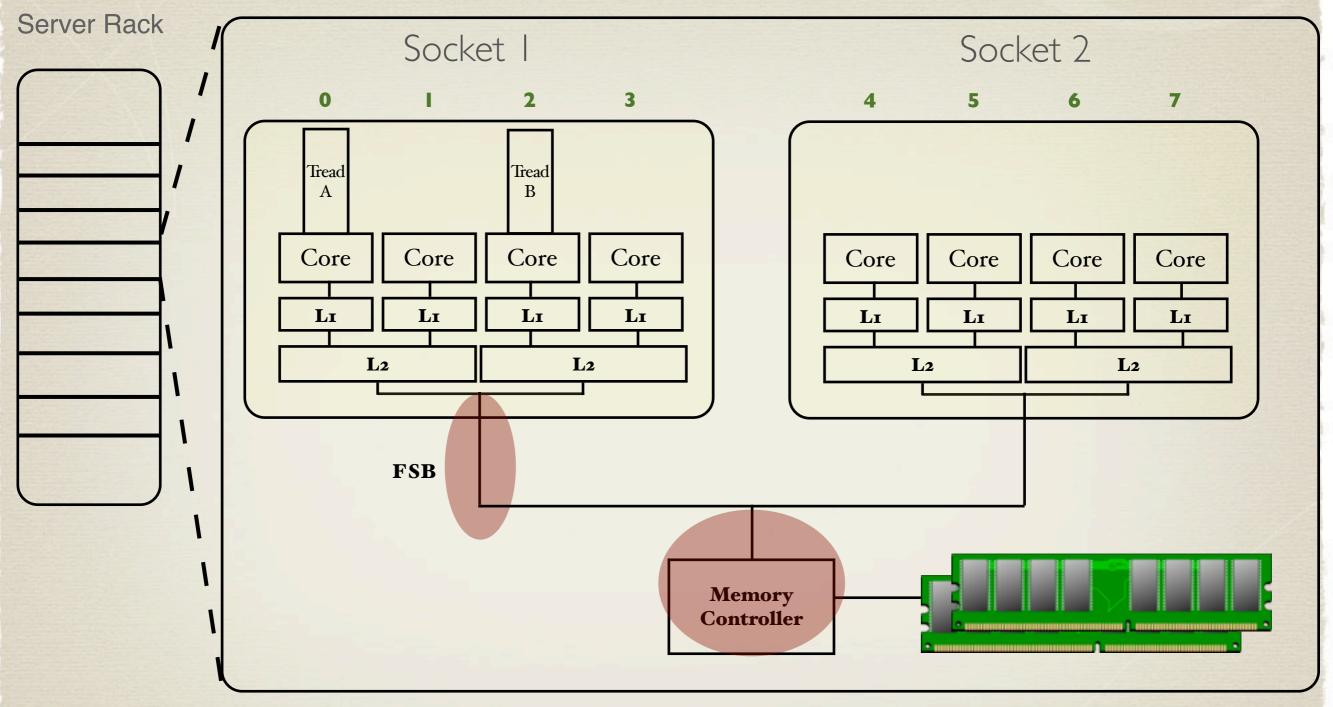

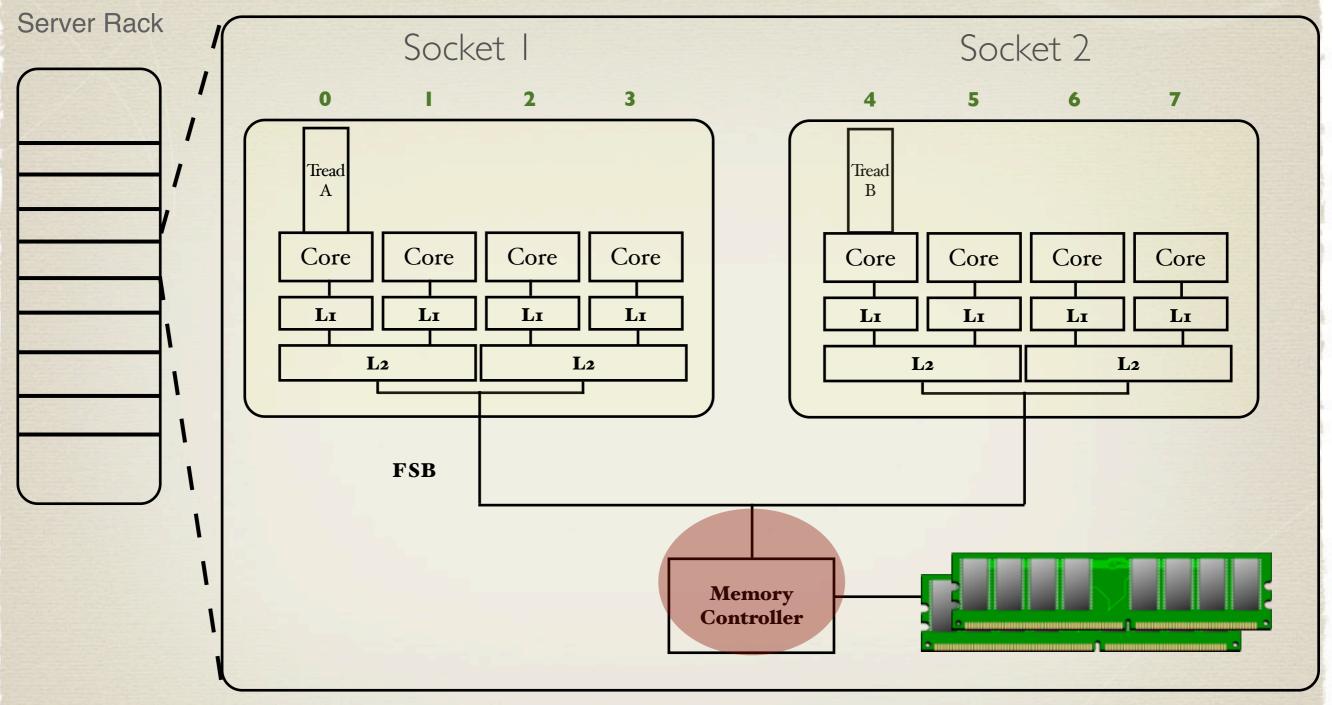

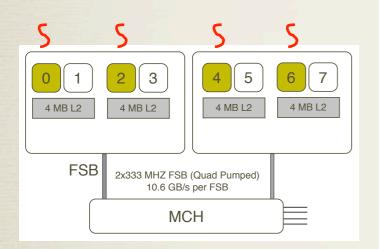

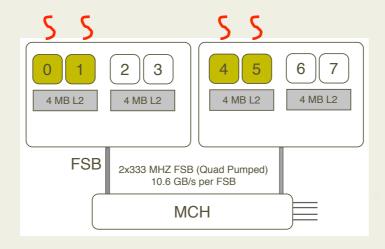

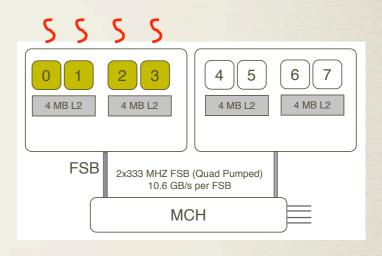

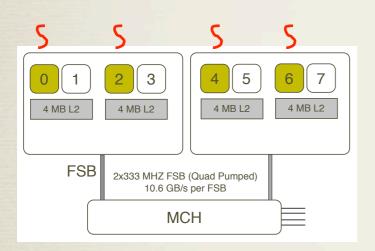

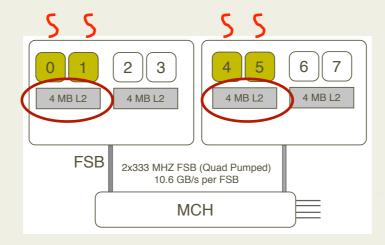

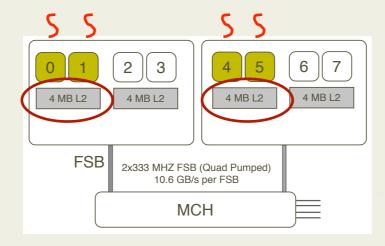

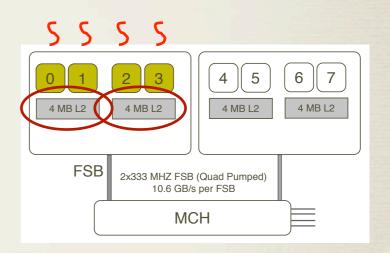

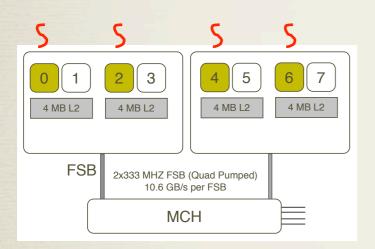

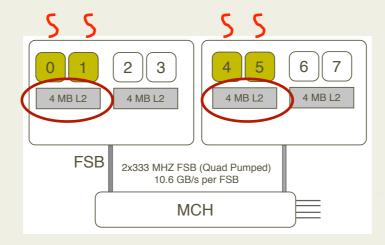

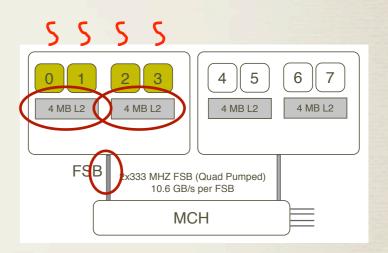

Intel Xeon(clovertown)

\* Thread-to-core mapping

\* Sharing: constructive and destructive

Intel Xeon(clovertown)

\* Thread-to-core mapping

\* Sharing: constructive and destructive

Intel Xeon(clovertown)

\* Thread-to-core mapping

\* Sharing: constructive and destructive

Intel Xeon(clovertown)

\* Thread-to-core mapping

\* Sharing: constructive and destructive

Intel Xeon(clovertown)

\* Thread-to-core mapping

\* Sharing: constructive and destructive

Intel Xeon(clovertown)

\* Thread-to-core mapping

Lingjia Tang: <a href="mailto:ltt8f@cs.virginia.edu">lt8f@cs.virginia.edu</a>

# Goals

- \* Characterize datacenter workloads

- \* Impact of memory resource sharing

- \* On-chip shared caches, memory bandwidth

- \* Intelligent Thread-to-Core mapper:

- \* Exploit workload characteristics

- \* Arrive at efficient TTC mapping

- \* Based on basic resource requirements.

- \* Applications

- \* may run alone

- \* may co-located with others

- \* Cache and bandwidth topology oblivious

- \* Based on basic resource requirements.

- \* Applications

- \* may run alone

- \* may co-located with others

- \* Cache and bandwidth topology oblivious

- \* Based on basic resource requirements.

- \* Applications

- \* may run alone

- \* may co-located with others

- \* Cache and bandwidth topology oblivious

- \* Based on basic resource requirements.

- \* Applications

- \* may run alone

- \* may co-located with others

- \* Cache and bandwidth topology oblivious

#### Outline

- \* Problem, Motivation and Background

- \* Characterization

- \* Intra-application Sharing

- \* Inter-application Sharing

- \* Varying number of threads and architectures

- \* Thread-to-Core Mapping

- \* Heuristic-based mapping

- \* Adaptive mapping

#### Benchmarks

| application      | description                                                                                                         | metric                | type                  |

|------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|

| content-analyzer | content and semantic analysis, used to take key words or text documents and cluster them by their semantic meanings | throughput            | latency-<br>sensitive |

| bigtable         | storage software for massive amount of data                                                                         | average<br>latency    | latency-<br>sensitive |

| websearch        | industry-strength internet search engine                                                                            | queries per<br>second | latency-<br>sensitive |

| stitcher         | image processing and stitching, used for generating street views                                                    | N/A                   | batch                 |

| protobuf         | protocol buffer                                                                                                     | N/A                   | batch                 |

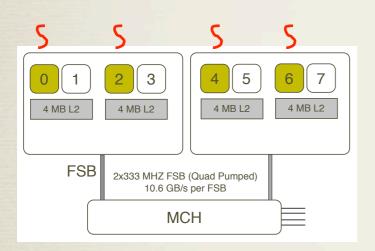

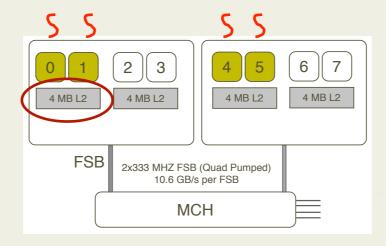

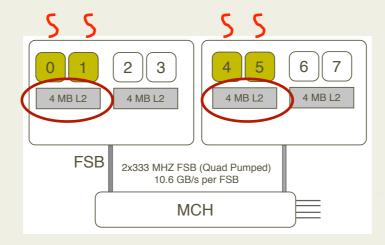

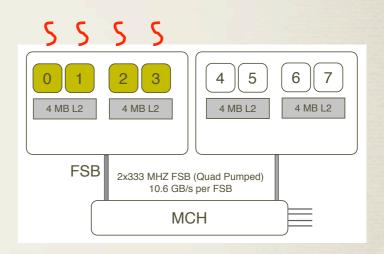

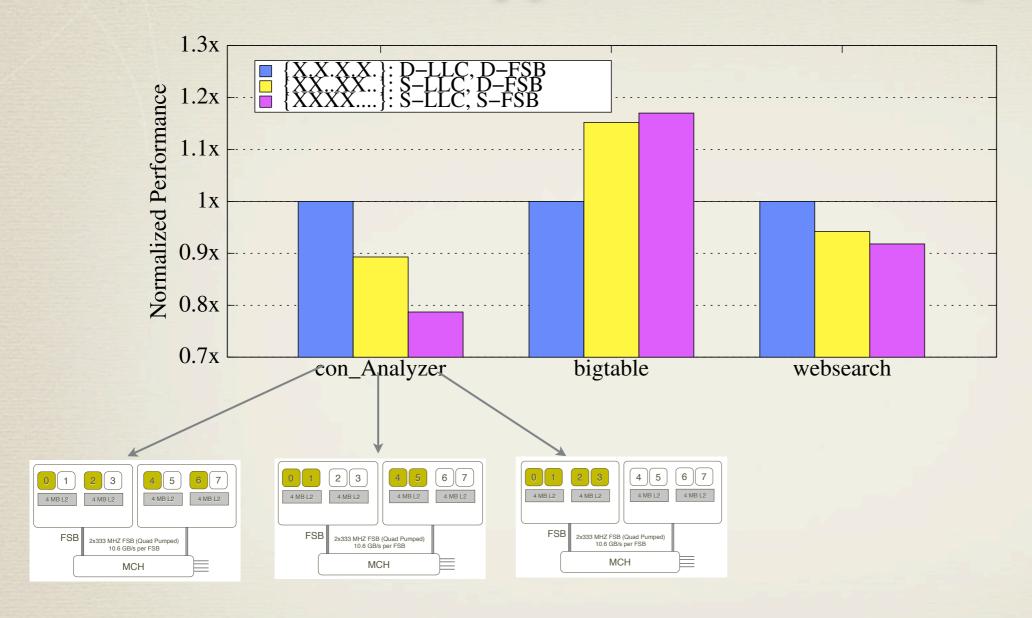

- \* Characterization Methodology

- \* 4 Threads, 3 Configurations

Separate Cache Separate FSB X.X.X.X.

Shared Cache Separate FSB XX..XX..

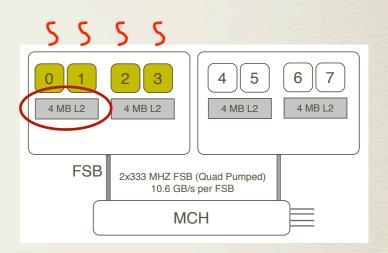

- \* Characterization Methodology

- \* 4 Threads, 3 Configurations

Separate Cache Separate FSB X.X.X.X.

Shared Cache Separate FSB XX..XX..

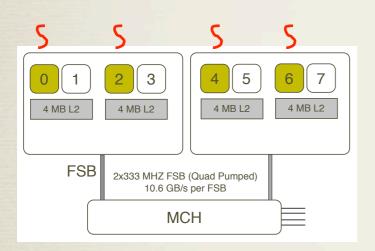

- \* Characterization Methodology

- \* 4 Threads, 3 Configurations

Separate Cache Separate FSB X.X.X.X.

Shared Cache Separate FSB XX..XX..

- \* Characterization Methodology

- \* 4 Threads, 3 Configurations

Separate Cache Separate FSB X.X.X.X.

Shared Cache Separate FSB XX..XX..

- \* Characterization Methodology

- \* 4 Threads, 3 Configurations

Separate Cache Separate FSB X.X.X.X.

Shared Cache Separate FSB XX..XX..

- \* Characterization Methodology

- \* 4 Threads, 3 Configurations

Separate Cache Separate FSB X.X.X.X.

Shared Cache Separate FSB XX..XX..

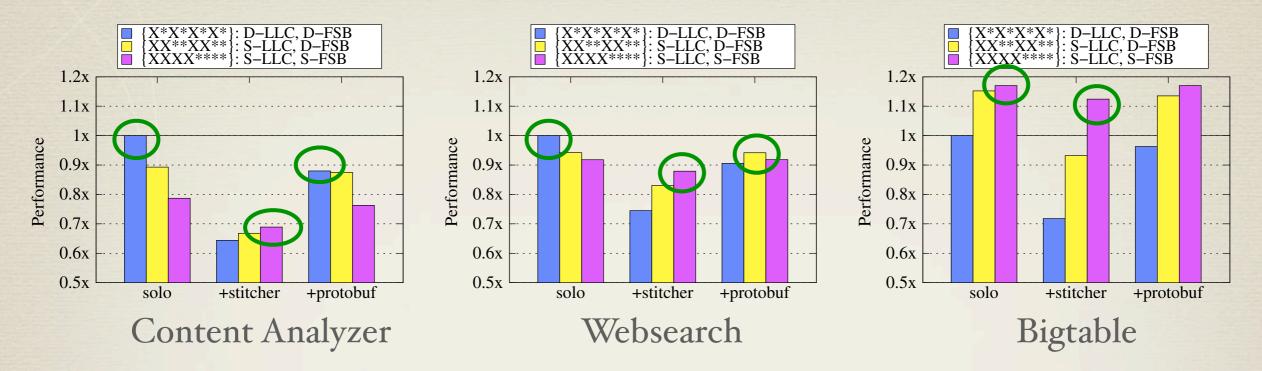

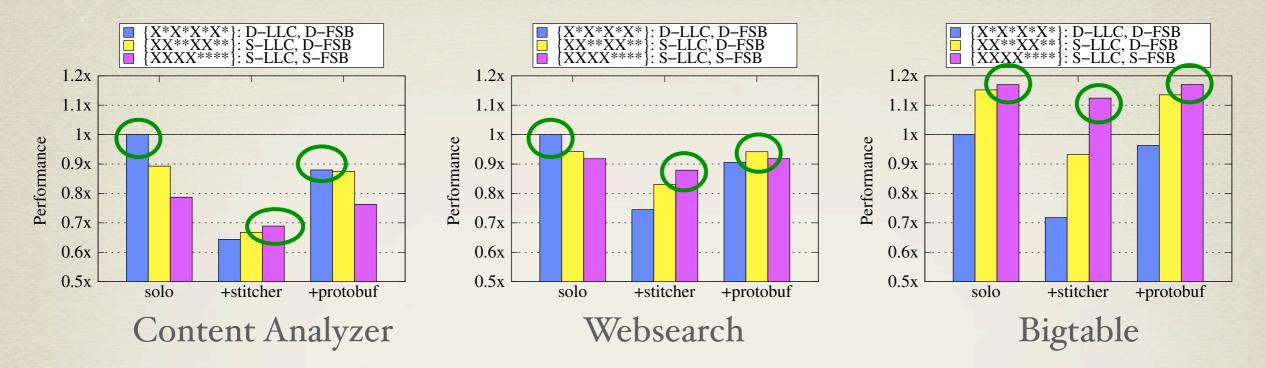

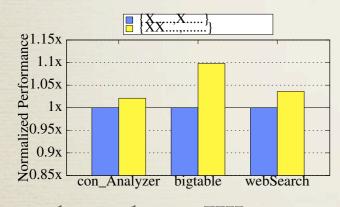

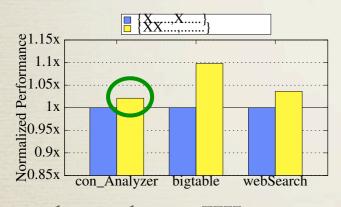

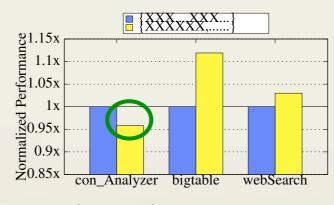

- \* Big performance swing (up to 22%)

- \* Both constructive and destructive

IO

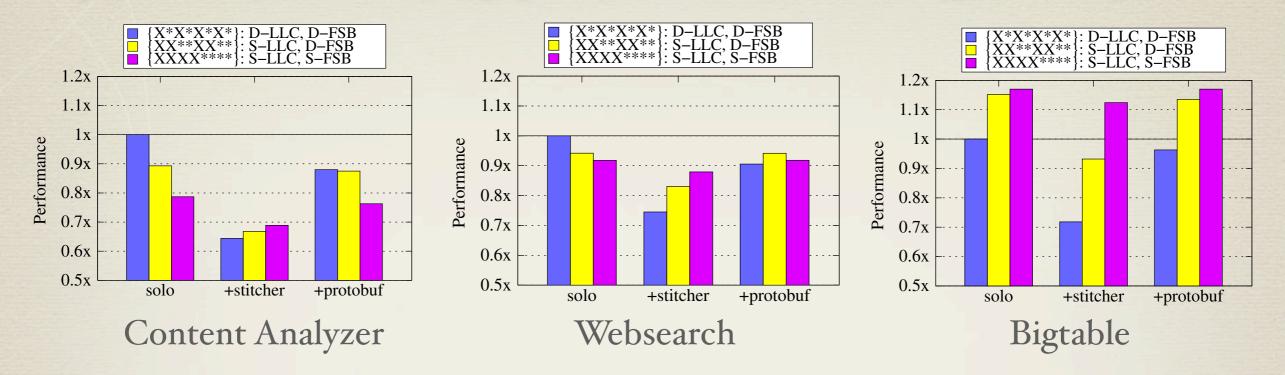

\* Bigtable benefits from cache sharing

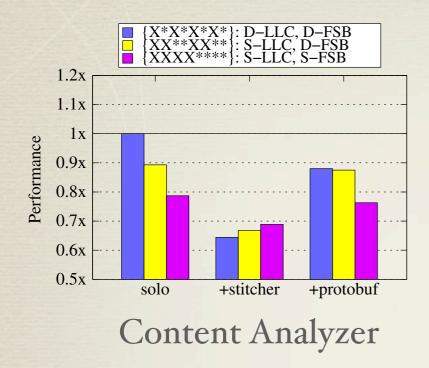

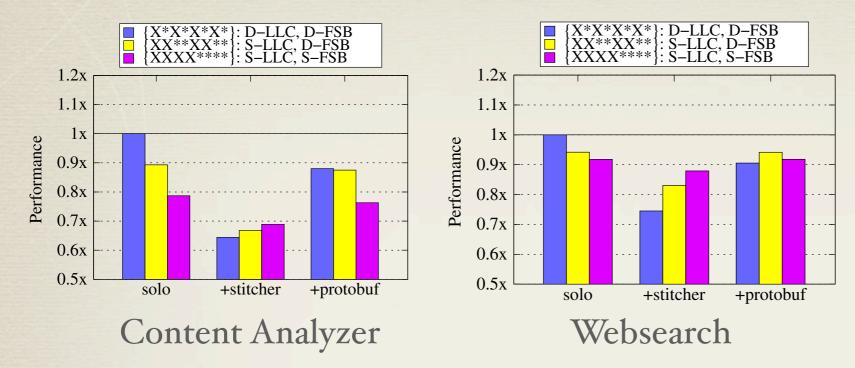

\* Con\_Analyzer and websearch: cache contention and bandwidth contention

\* Intra-application \langle

- \* significant (22%)

- both constructive and destructive

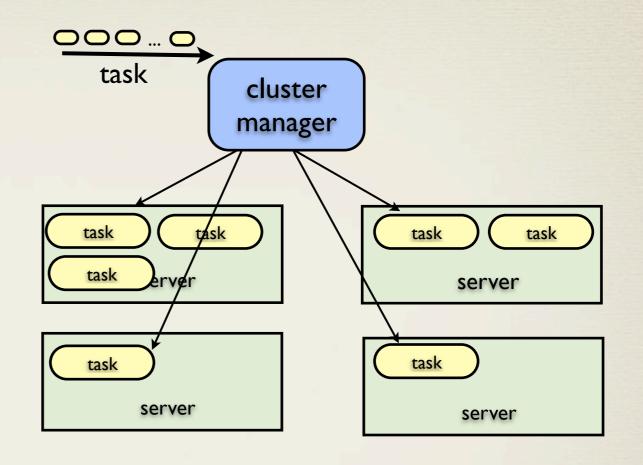

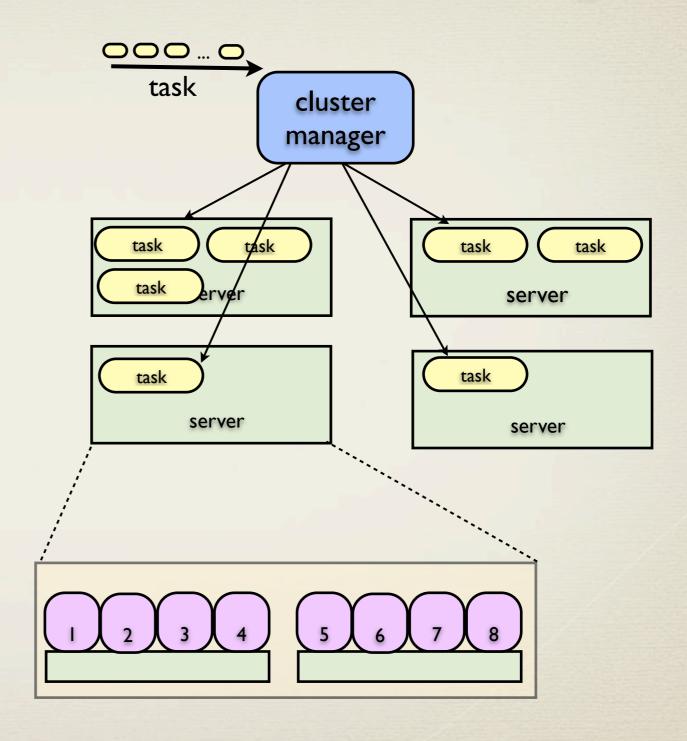

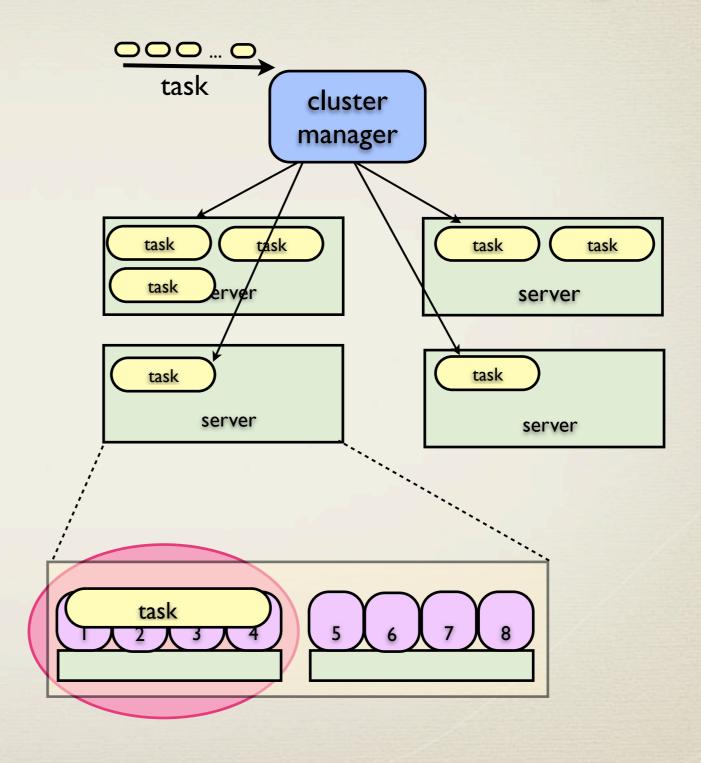

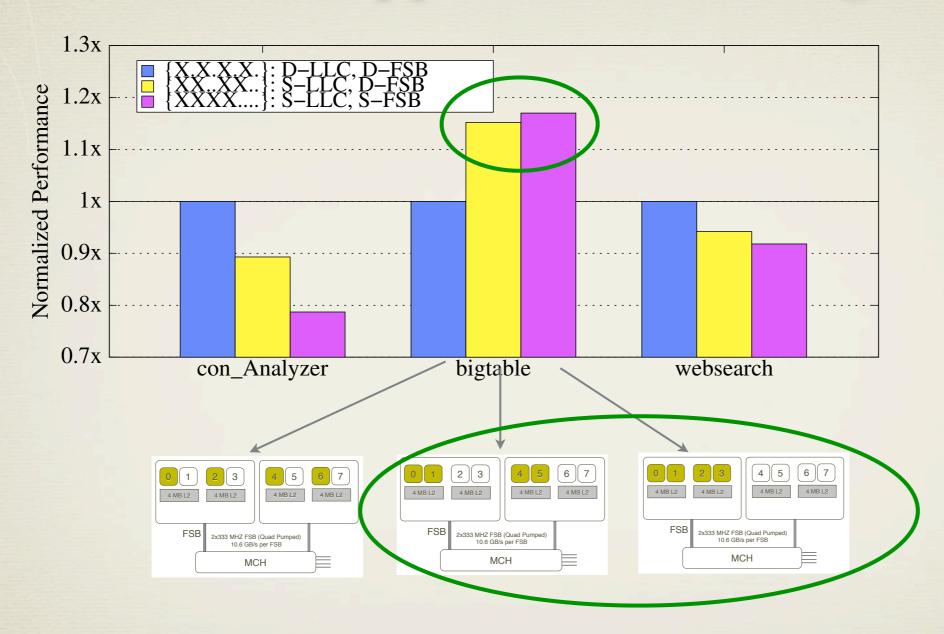

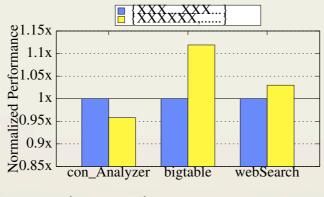

- \* Inter-application

- \* Colocation of multiple applications

- \* What's the impact of resource sharing between applications?

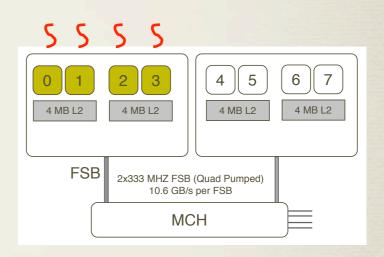

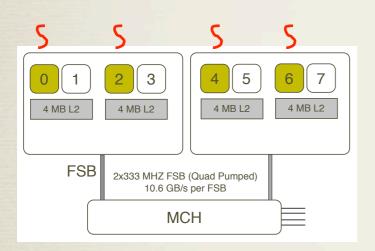

- \* Characterization Methodology

- \* 2 Applications, 8 Threads (4/4), 3 Configurations

- \* Characterization Methodology

- \* 2 Applications, 8 Threads (4/4), 3 Configurations

14

Lingjia Tang: <a href="mailto:lt8f@cs.virginia.edu">lt8f@cs.virginia.edu</a>

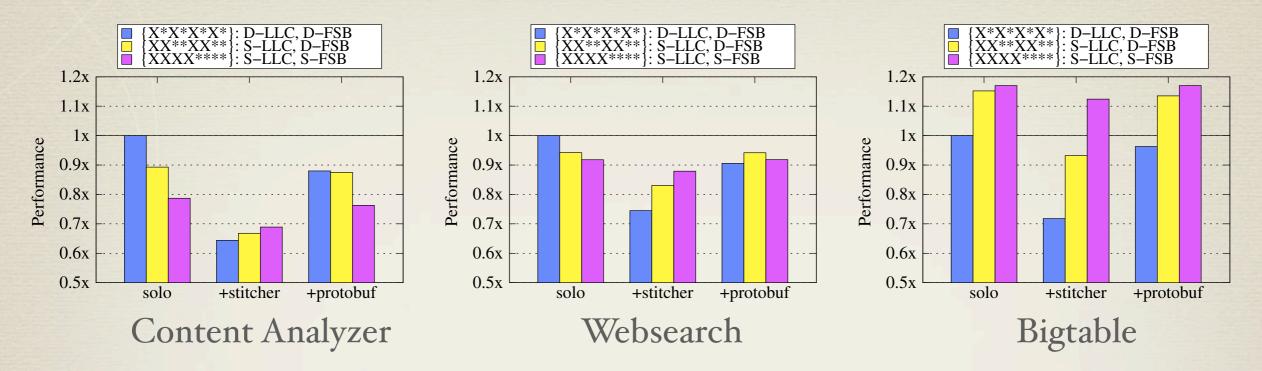

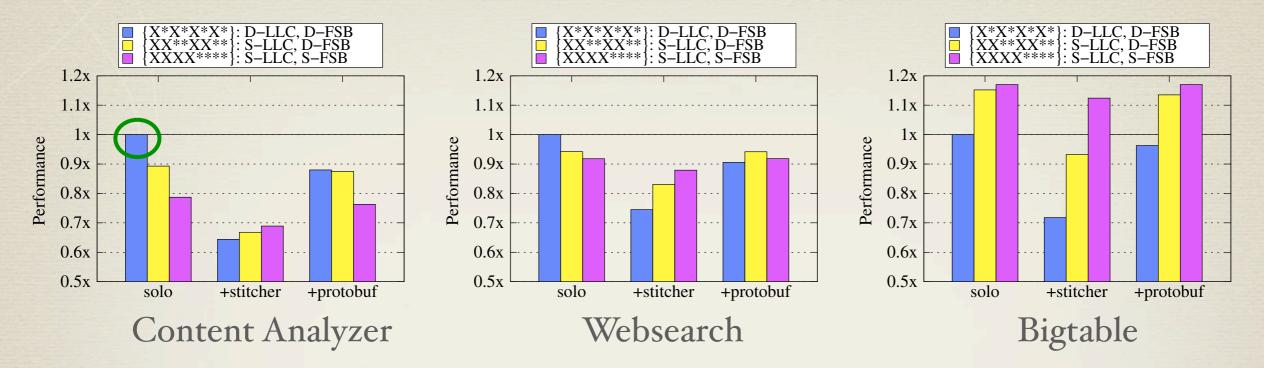

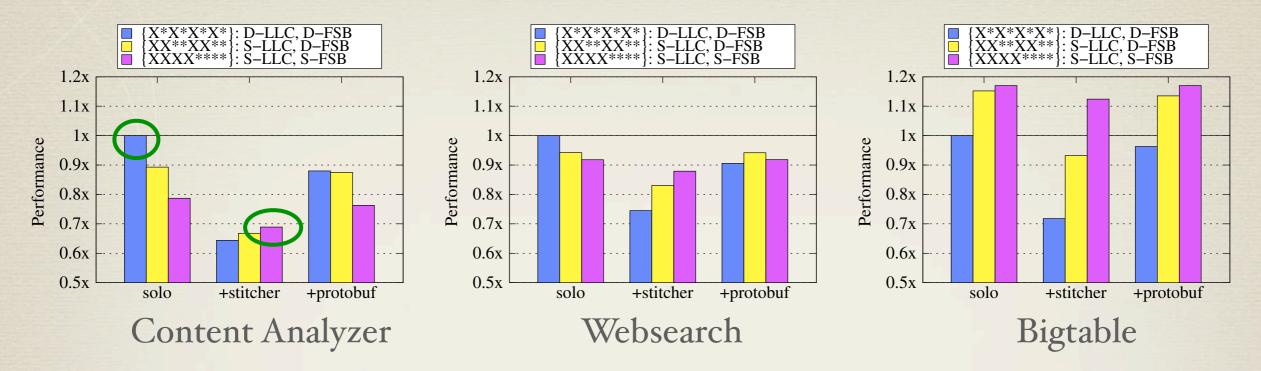

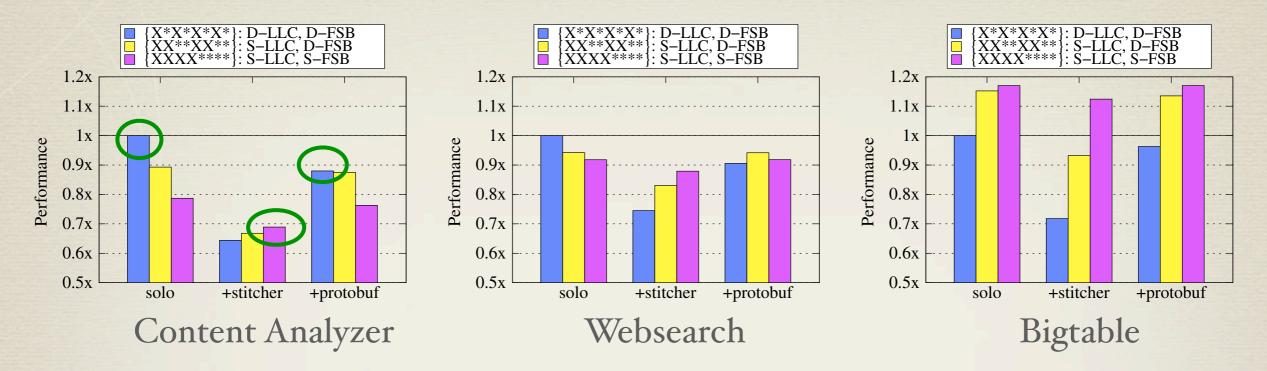

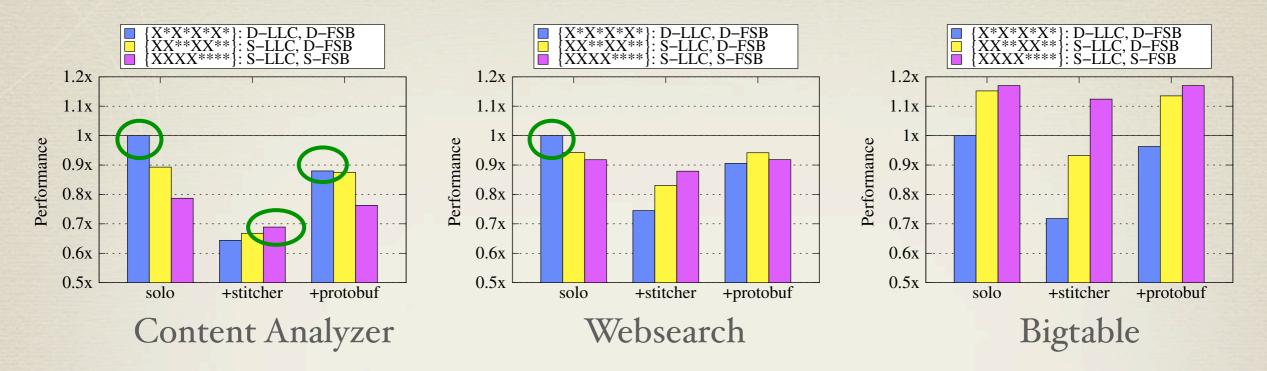

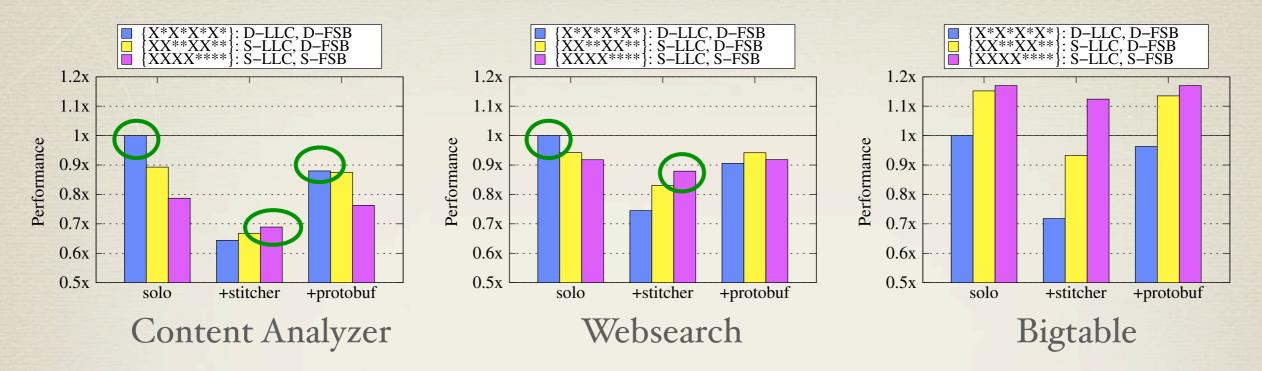

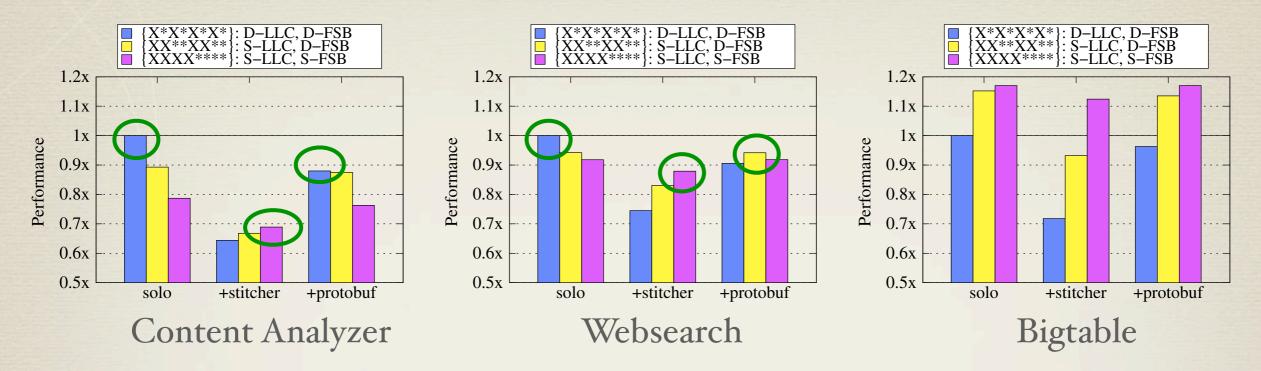

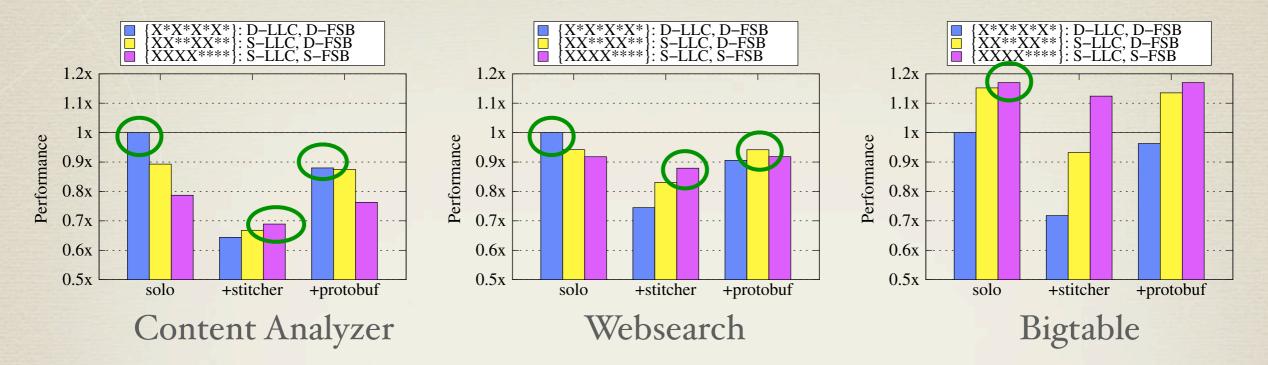

\* Performance Degradation

\* Performance Degradation

\* Performance Degradation

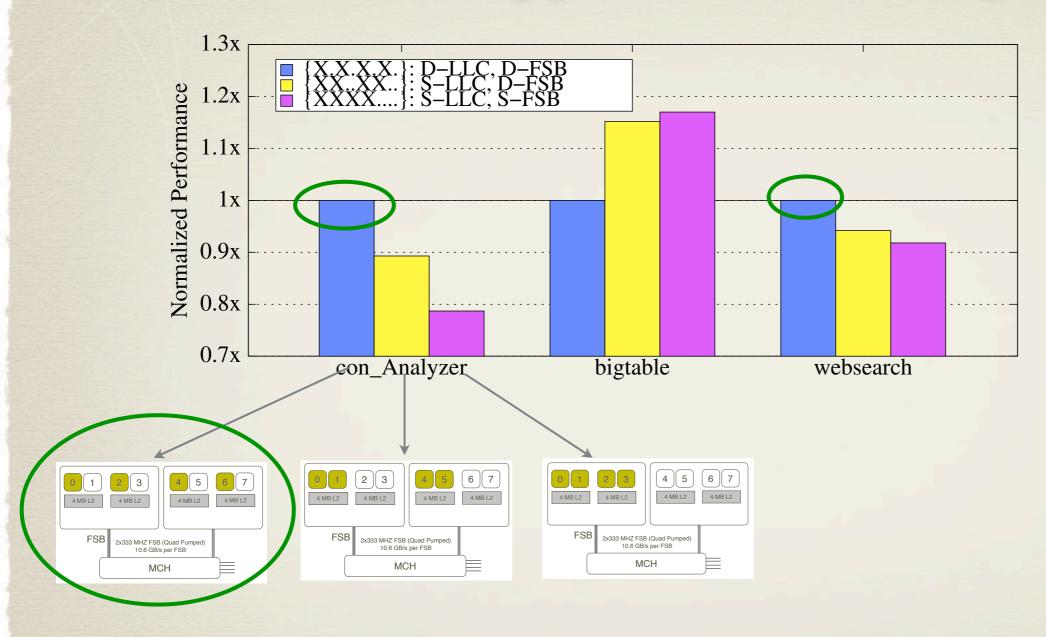

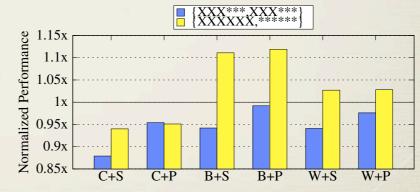

- \* Optimal mapping changes when co-runner changes

- \* Difference can be significant

- \* Optimal mapping changes when co-runner changes

- \* Difference can be significant

- \* Optimal mapping changes when co-runner changes

- \* Difference can be significant

- \* Optimal mapping changes when co-runner changes

- \* Difference can be significant

- \* Optimal mapping changes when co-runner changes

- \* Difference can be significant

- \* Optimal mapping changes when co-runner changes

- \* Difference can be significant

- \* Optimal mapping changes when co-runner changes

- \* Difference can be significant

- \* Optimal mapping changes when co-runner changes

- \* Difference can be significant

- \* Optimal mapping changes when co-runner changes

- \* Difference can be significant

- \* Optimal mapping changes when co-runner changes

- \* Difference can be significant

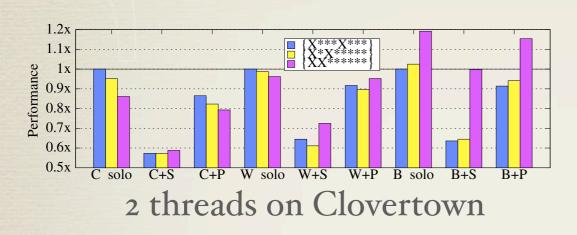

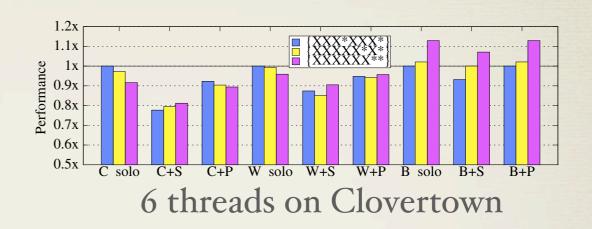

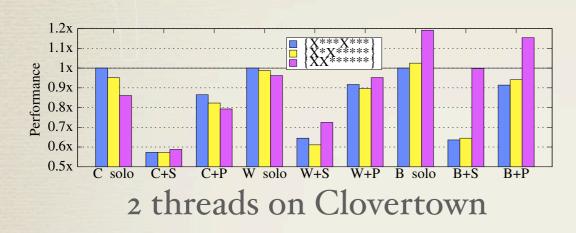

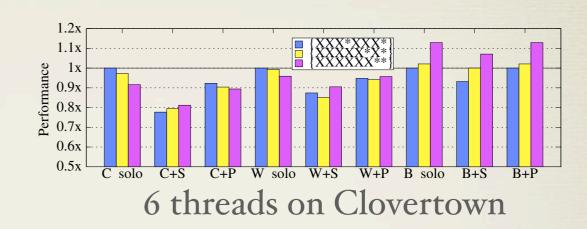

## Varying Number of Threads and Architecture

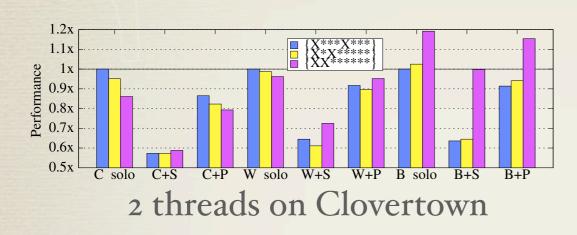

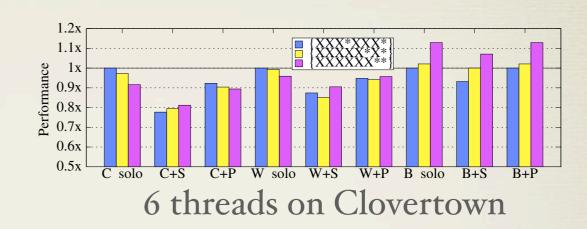

#### Varying Thread Count

#### Varying Architecture

2 threads on Westmere

4 threads on Westmere

6 threads on Westmere

\* Impact from sharing changes when architecture changes.

## Varying Number of Threads and Architecture

#### Varying Thread Count

#### Varying Architecture

2 threads on Westmere

4 threads on Westmere

6 threads on Westmere

\* Impact from sharing changes when architecture changes.

### Varying Number of Threads and Architecture

#### Varying Thread Count

#### Varying Architecture

2 threads on Westmere

4 threads on Westmere

6 threads on Westmere

\* Impact from sharing changes when architecture changes.

### Outline

- \* Problem, Motivation and Background

- \* Characterization

- \* Intra-application Sharing

- \* Inter-application Sharing

- \* Varying architectures

- \* Thread-to-Core Mapping

- \* Heuristic-based mapping

- \* Adaptive mapping

18

# Thread-to-Core Mapping

- \* Heuristics-based Approach

- \* Identify sharing and contention properties

- \* Map threads accordingly

- \* Adaptive Approach

- \* Searching for the optimal mapping online

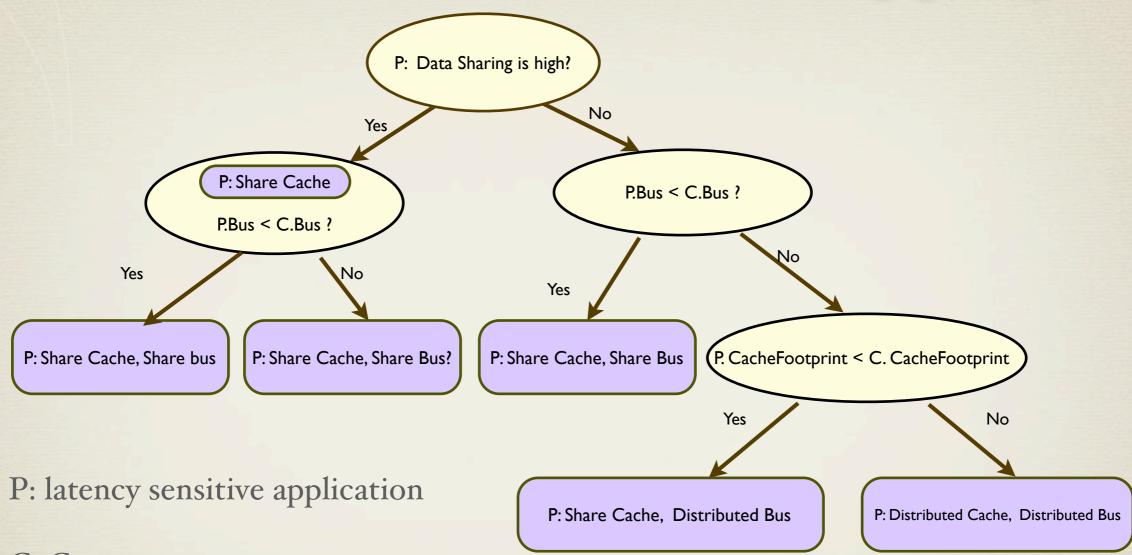

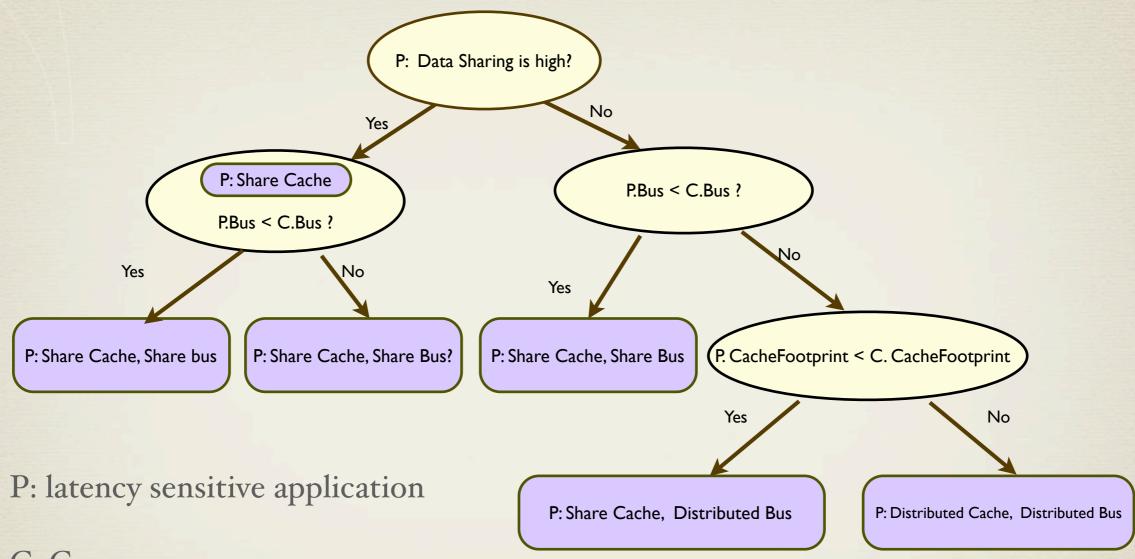

## Heuristic-based TTC Mapping

- \* Mapping based on application's characteristics and resource topology

- \* Data Sharing

- \* Cache usage

- \* Bandwidth usage

- \* Colocation: prioritize latency-sensitive applications

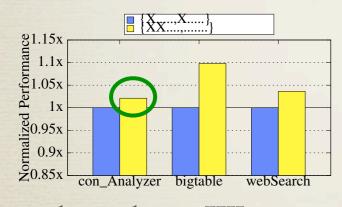

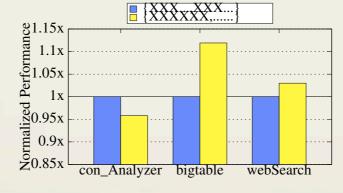

## Heuristic-based TTC Mapping

\* C: Corunner

## Heuristic-based TTC Mapping

- \* C: Corunner

- \* Pros: analytical, known applications

- \* Cons: architecture specific; may require profiling

2.T

Lingjia Tang: <a href="mailto:lt8f@cs.virginia.edu">lt8f@cs.virginia.edu</a>

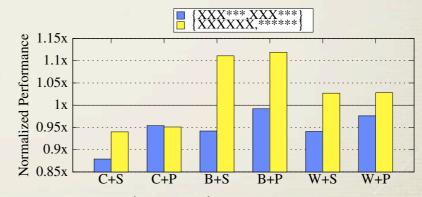

## Adaptive TTC Mapping

- \* Insight: Optimal mapping changes when co-runner changes, when number of threads and architecture changes

- \* Competition Heuristics

- \* Learning Phase

- \* Execution Phase

- \* Datacenter applications:

- \* Steady phases

- \* Co-runner may change

- \* Architecture may change

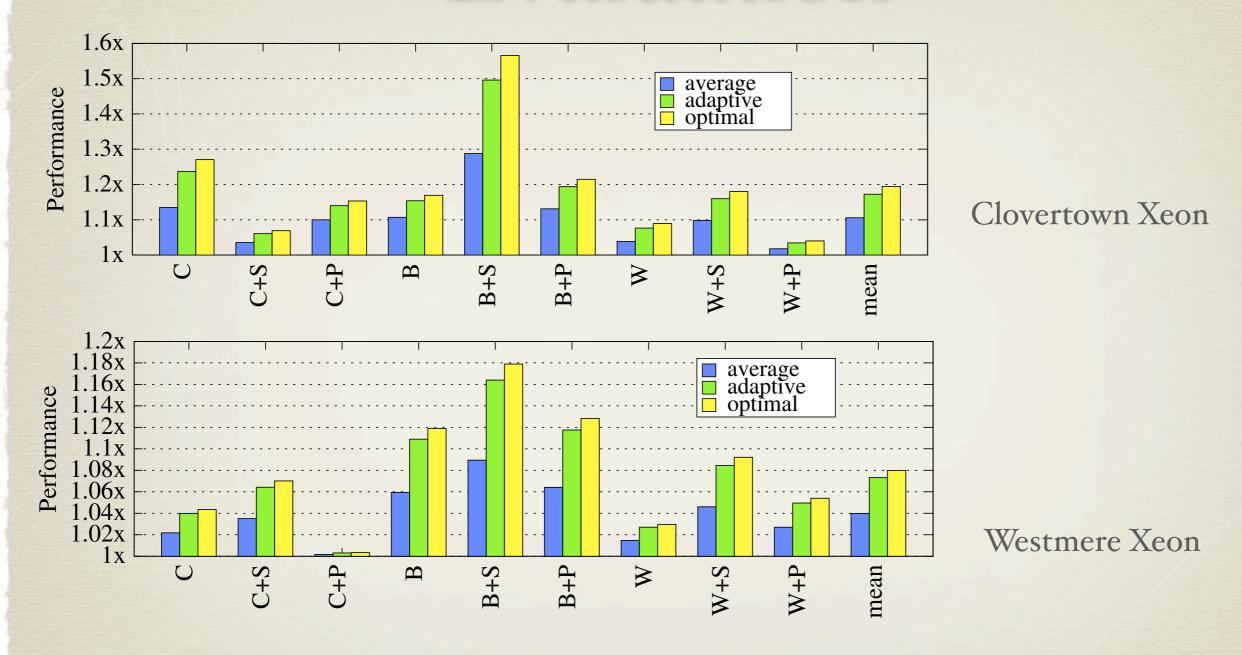

## Evaluation

\* Outperforms the average random mapping by up to 20%

## Conclusion

- \* Memory resource sharing has significant impact on datacenter applications (both constructive and destructive)

- \* Performance swing up to 40% simply based on thread-to-core mapping.

- \* Optimal thread-to-core mapping changes when corunner changes.

- \* Importance of intelligent TTC mapping: adaptive

Lingjia Tang: www.lingjia.org

Jason Mars: www.jasonmars.com